2015年4月

Journal of Terahertz Science and Electronic Information Technology

Apr., 2015

文章编号: 2095-4980(2015)02-0226-07

### 宽带单载波频域均衡系统设计与 FPGA 实现

杨 刚,李 莹,张小飞\*,徐大专

(南京航空航天大学 电子信息工程学院, 江苏 南京 210016)

摘 要:单载波频域均衡(SC-FDE)是数字通信中克服多径衰落的有效技术。宽带通信系统中应用单载波频域均衡系统设计,实现137.5 MHz 载波下27.5 Mbps的码元传输速率。同时在系统中添加1/2 码率卷积码与(239,223)里德-所罗门(RS)码的级联信道纠错编码,提高系统的可靠性。完成单载波频域均衡系统设计,分析设计系统的关键技术,最终在现场可编程门阵列硬件平台上进行系统实现、调试和验证,完成系统实际误码率的测试。

关键词:宽带单载波频域均衡;卷积码;里德-所罗门码;现场可编程门阵列设计

中图分类号: TN914.3

文献标识码:A

doi: 10.11805/TKYDA201502.0226

# Broadband Single Carrier-Frequency Domain Equalization system design and FPGA implementation

YANG Gang, LI Ying, ZHANG Xiaofei\*, XU Dazhuan

(College of Electronic and Information Engineering, Nanjing University of Aeronautics and Astronautics, Nanjing Jiangsu 210016, China)

Abstract: Single Carrier-Frequency Domain Equalization(SC-FDE) is effective to overcome multipath fading in digital communication and it is widely used for its performance. SC-FDE is adopted in broadband communication systems and a symbol transmission rate of 27.5 Mbps is realized under the carrier frequency of 137.5 MHz. The concatenated channel error correction coding of 1/2 rate convolution code combined with (239,223) Reed-Solomon(RS) code is used in order to improve the reliability of the system. The SC-FDE system is designed, and the key technologies of this system are analyzed. It is implemented on Field Programmable Gate Array(FPGA) hardware platform. The commissioning and validation are performed as well. The actual Bit Error Ratio(BER) test of the system is executed.

**Key words:** broadband Single Carrier-Frequency Domain Equalization(SC-FDE); convolution code; Reed-Solomon(RS) code; Field Programmable Gate Array(FPGA) design

在现代无线数字通信系统中,信号的传输从窄带变为宽带,而宽带无线通信的信道是频率选择性衰落的多径信道。多径效应引起的时延扩展导致严重的符号间干扰(Inter Symbol Interference, ISI),严重影响通信的可靠性,因此需要采用一种有效的方法抵抗信道的影响<sup>[1]</sup>。目前提出的方法主要有:单载波时域均衡(Single Carrier Time Domain Equalization, SC-TDE)、单载波频域均衡(Single Carrier Frequency Domain Equalization, SC-FDE)和正交频分复用(Orthogonal Frequency Division Multiplexing, OFDM)技术。SC-TDE 在接收端采用一个自适应均衡器来补偿符号间干扰<sup>[2]</sup>。它的主要部件就是一个或多个横向滤波器,而横向滤波器抽头系数的数目由多径时延来确定。在高速无线通信系统中较大的时延会导致复杂度很高。3GPP(3rd Generation Partnership Project)的长期演进计划中,提出了上行采用单载波技术,下行采用 OFDM 技术的方案。

OFDM 系统在发射端通过快速傅里叶逆变换(Inverse Fast Fourier Transform, IFFT)将数据符号并行调制到正交的子载波上,克服了频率选择性衰落造成的影响,在频域实现均衡。其频谱利用率高,系统复杂度较低(与信道最大时延扩展的对数成正比),但是它对定时误差和载波同步敏感,且每个 OFDM 符号的多路子载波在时域叠

收稿日期: 2014-06-12; 修回日期: 2014-07-24

基金项目: 国家自然科学基金资助项目(61371169); 江苏省博士后科研资助计划项目(1201039C); 中国博士后基金资助项目(2012M521099); 江 苏高校优势学科建设工程资助项目

<sup>\*</sup>通信作者: 张小飞 email:zhangxiaofei@nuaa.edu.cn.

加会产生很大的峰值平均功率比,因而对射频前端的要求较高。SC-FDE 技术综合了 OFDM 技术和单载波传输的 优点<sup>[3-5]</sup>,同时文献[6]分析指出对于一般的 SC-FDE 和 OFDM 系统,在低信噪比下 OFDM 系统的误码性能略优于 SC-FDE 系统,而在高信噪比下,SC-FDE 系统要优于 OFDM 系统。本文设计的系统可以实现 137.5 MHz 载波下的 27.5 Mbps 码元传输速率,实现了宽带 SC-FDE 系统。

#### 1 系统设计

#### 1.1 SC-FDE 系统模型

在传统的单载波系统中,接收机主要由 A/D 变换、混频滤波、信道估计、信道均衡等模块组成<sup>[7-8]</sup>。本文在单载波频域均衡传输系统中添加了信道编译码模块,以获得更好的误码率性能。系统采用的是 1/2 码率的卷积码和 RS 码级联的方案。为提高系统的传输速率,使用了正交相移键控(Quadrature Phase Shift Keying, QPSK)的调制方式,系统框图见图 1。

Fig.1 System diagram of SC-FDE 图 1 SC-FDE 系统框图

#### 1.2 系统帧结构

单载波频域均衡系统中使用的数据帧结构是基于独特字(Unique Word, UW)的帧结构,接收端使用 UW 完成帧同步、信道估计、循环前缀的功能。而作为 UW 的序列应该满足在时域上和频域上均具有较小的起伏。常用的 UW 字有 Newsman 序列、Frank-Zadoff 序列等。本文使用的是伪叠加序列(Zadoff-Chu)序列,其定义为:

$$\theta_{\text{Chu}}(k) = \exp\left\{-j2\pi \frac{r}{N} \left[\frac{k(k+1)}{2} + qk\right]\right\}, \quad k=0,1,2,\dots,N-1, \quad N \Rightarrow 5$$

(1)

式中:N表示序列长度:r是与N互质的正整数:q取任意值。

Zadoff-Chu 序列的算法在各种信道环境下的性能都很优越, Zadoff-Chu 序列具有良好的周期自相关和互相关特性, 其幅值恒定, 并且具有傅里叶变换保持特性。

系统传输帧由 2 个完全相同的 64 位 Zadoff-Chu 序列和 1 920 个数据位构成,见图 2。每一帧起始位置的 2 段 Zadoff-Chu 序列用来充当循环前缀,完成帧同步、信道估计、噪声估计等功能。数据帧连续传输<sup>[9]</sup>。

## Chu sequence (64 bit) Chu sequence (64 bit) data (1 920 bit)

Fig.2 System frame structure 图 2 系统帧结构

#### 2 宽带单载波频域均衡系统中关键技术

#### 2.1 帧同步与频偏估计

本设计利用 UW 完成帧同步,对接收到的每一帧头部的 2 段 64 位 Zadoff-Chu 序列与本地的 Zadoff-Chu 序列做相关运算,由于序列自相关特性,会得到一对相关峰(理想情况)或一对主峰和若干对副峰(存在多径)。根据相关峰完成峰值搜索,最终完成信号帧同步[10]。

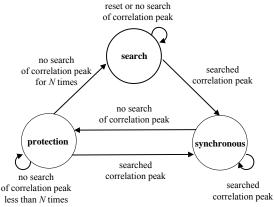

帧同步采用有限状态机设计完成。状态机的实现采用 了基于搜索态-同步态-保护态的三态同步机制,见图 3。

频偏估计同样采用搜索到的相关峰来完成,假设载波频偏为 $\Delta f$ ,每帧有N个符号,每个符号的周期为T。设当前帧的主相关峰为p(n),前一帧的主相关峰为p(n-1),则

Fig.3 Three states synchronization 图 3 三态同步图示

2个主峰的相位差满足:

$$\Delta \varphi = 2\pi \Delta f N = \arctan \left[ p(n) p^*(n-1) \right]$$

(3)

式中:  $\Delta \varphi$  表示相位差; arctan 表示取反正切角;  $p^*$ 表示取 p 的共轭值。 载波的频偏为:

$$\Delta f = \frac{1}{2\pi N} \arctan\left[p(n)p^*(n-1)\right] = \frac{1}{2N} \frac{\operatorname{Im}\left[p(n)p^*(n-1)\right]}{\operatorname{Re}\left[p(n)p^*(n-1)\right]}$$

(4)

式中: Re[]表示取复数的实部; Im[]表示取复数的虚部。

由于相偏相对较小,实际设计中可以只使用虚部完成计算,以降低复杂度。设计帧长度为 2 048 位,故采用本方法所能纠正的最大频偏为:  $|\Delta f| = \frac{1}{2\Delta t} = \frac{27.5}{2 \times 2.048} \, \mathrm{MHz} \approx 6.7 \, \mathrm{kHz}$ 。

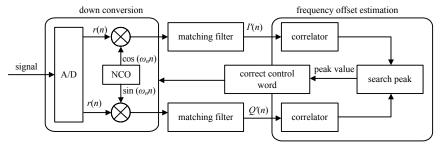

同步与频偏估计的实现框图见图 4。

Fig.4 Synchronization and frequency offset estimation 图 4 同步与频偏估计

#### 2.2 信道估计和均衡

系统利用 UW 完成信道估计,接收信号为:

$$r(n) = h(n) * s_{\text{Chu}}(n) + w(n)$$

$$\tag{5}$$

式中: h(n)为信道冲击响应;  $s_{Chu}(n)$ 为发送 Zadoff-Chu 序列; w(n)为信道加性噪声; \*表示卷积运算。 变换到频域表示为:

$$R(k) = H(k)S_{\text{Chu}(k)} + W(k) \tag{6}$$

取本地 Zadoff-Chu 序列的频域值  $S_{Chu}(k)$ 的共轭值  $S_{Chu}^*(k)$ 与 R(k)相乘,由 Zadoff-Chu 序列的横幅特性和与噪声不相关性可以得到  $R(k)S_{Chu}^*(k) = H(k)|S_{Chu}(k)|^2$ ,得到信道估计值[11]。

通过信道估计得到 H(k)以后,通过相应的均衡准则可以实现信道均衡。常用的频域均衡准则有迫零准则(Zero Forcing, ZF)和最小均方误差准则(Minimum Mean Square Error, MMSE)。 ZF 相对比较简单,将 H(k)作为均衡系数,若接收信号频域表示为 R(k),则最终均衡后信号为  $\hat{r}(n)$  = IFFT  $\frac{R(k)}{H(k)}$ 。

在 MMSE 准则中,接收信号可以表示为:

$$r(n) = \sum_{l=1}^{N} a_{j} h(nT - lT) + n(nT)$$

(7)

式中 n(nT)为均值为 0、方差为  $\sigma^2$ 的加性高斯白噪声抽样值。

均衡后信号可以表示为 $\hat{s}(n) = \frac{1}{N} \sum_{k=1}^{N} F(k) R(k) e^{\frac{i^2 \pi}{N} kn}$ ,误差信号为 $e = \hat{s}(n) - s(n)$ ,s(n)表示信号的真实值,则误差均值表示为:

$$E(|e|^{2}) = \frac{P}{N} \sum_{k=1}^{N} |F(k)H(k) - 1|^{2} + \frac{\sigma^{2}}{N} \sum_{k=1}^{N} |F(k)|^{2}$$

(8)

式中:P表示信号发射功率;F(k)表示系统所需的均衡系数。

根据 MMSE 准则,可以得到

$$F(k) = \frac{H(k)^*}{\frac{\sigma^2}{P} + \left|H(k)\right|^2}$$

,则均衡后信号为:

$$\hat{s}(n) = \text{IFFT} \left[ \frac{S(k)|H(k)|^2}{|H(k)|^2 + \frac{\sigma^2}{P}} + \frac{W(k)H^*(k)}{|H(k)|^2 + \frac{\sigma^2}{P}} \right]$$

(9)

由式(9)可以看出, MMSE 准则将信道状况和加性噪声都考虑在内,即使信道存在深衰落点,也不会因为过零问题造成均衡结果的严重误差<sup>[12]</sup>。

#### 2.3 信道译码

级联码可以获得更高的性能,本文级联码采用以卷积码作为内码,RS 码作为外码的结构。卷积码充分利用了各码段的相关性,并且可以相对较容易地实现最佳译码,而RS 码是线性分组码的一种,对突发错误和随机错误有很强的纠错能力,这两者的级联编码广泛应用在深空通信和卫星通信中[13]。

卷积码的译码采用 Viterbi 译码。Viterbi 译码实际上是基于卷积码网格图的最大似然译码,相对于门限译码和序列译码有更优的性能<sup>[14]</sup>。RS 码的译码比较复杂,主要过程分为以下几步:a) 由接收到的信号 r(x)计算伴随式 s,若伴随式为 0 则没有错误,否则继续下面的步骤;b) 根据 s 求得错误位置多项式  $\Delta(x)$ ;c) 采用钱氏搜索法求解  $\Delta(x)$  的根,确定错误位置;d) 由错误位置计算得到错误值,获得错误图样  $\hat{e}$  ;5)  $r(x) - \hat{e}$ ,完成纠错  $\hat{e}$  [15-17]。

#### 3 FPGA 实现与测试

#### 3.1 FPGA 实现

系统在 XILINX 的 xc4vlx160 上完成设计验证、调试和实际测试。系统实际测试见图 5, 一台电脑与安捷伦 E4438C 相连接,通过 matlab 设计发射机控制矢量信号发生器产生发射波形。发射机设计载波频率为 137.5 MHz, 符号速率为 27.5 Mbps,系统采用 QPSK 调制来增加传信率。信道编码模块使用码率为 1/2 的卷积码与(239,223)RS 码级联的方式。E4438C 的 RF 端口连接到硬件平台的 ADC 接口,通过示波器和另一台电脑上安装的 chipscope 观测接收机的各项信息,完成验证和测试。系统接收机主要由以下几部分构成:模拟前端、频偏估计、帧同步、频域信道估计和均衡、信道译码。

Fig.5 System practical test 图 5 系统实际测试

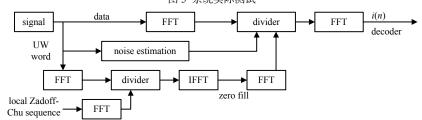

Fig.6 Frequency domain channel estimation and equalization 图 6 频域信道估计和均衡

频域信道估计和均衡是系统中较复杂的部分,涉及到 FFT、IFFT、除法器、乘法器、RAM、ROM 等 XILINX IP 核。硬件实现结构见图 6。均衡时,需要对接收帧做 2 048 点的 FFT 和 IFFT,这导致系统硬件开销和时间开销很大,难以满足实时处理的要求,因此采用乒乓操作的结构,配置 FFT 核为基 4 突发模式。此举虽然增加了

硬件开销,但能够满足处理的时间需求。此外,鉴于除法器的硬件开销很大,在设计上使用查找表的方法将除法器转化为ROM+乘法器的结构来节省资源。

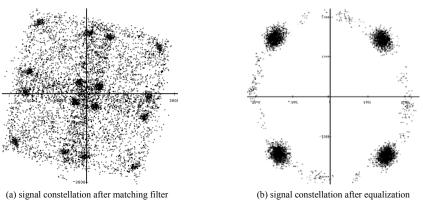

在多径能量-3 dB、延时 30 个符号的信道条件下均衡前后实际系统星座图对比如图 7(a)和图 7(b)。图中能明显看出均衡后信号的星座点汇聚成 4 个点。

Fig.7 Comparison of constellation before and after equalization 图 7 均衡前后星座图对比

经过信道均衡后的数据已经可以作为接收数据,但为了获得更高的系统性能,均衡后的数据还要经过信道译码模块。系统设计实现了 Viterbi 译码器和  $GF(2^8)$ 域中任意长度下纠正 8 或 4 个错误的 RS 译码器,本文不再详细介绍。

#### 3.2 测试结果

系统在硬件平台上完成实测验证,使用 Agilent E4438C 信号源获得发射信号,发射波形由 matlab 编写配置文件来完成,接收端设计误码率统计模块统计系统性能。系统共占用 FPGA 资源 40 344 个 Slice,占总量的 29%。

表 1 均衡后误码率统计

| $R_{\rm SN}/{ m dB}$ | BER          |                     |                     |                     |                     |                     |  |  |

|----------------------|--------------|---------------------|---------------------|---------------------|---------------------|---------------------|--|--|

|                      | delay 0      | delay of 10 symbols | delay of 20 symbols | delay of 30 symbols | delay of 40 symbols | delay of 50 symbols |  |  |

| 6.5                  | 0.003 03     | 0.028 27            | 0.028 61            | 0.026 16            | 0.033 82            | 0.041 18            |  |  |

| 7.0                  | 0.001 74     | 0.023 27            | 0.022 31            | 0.022 05            | 0.027 81            | 0.036 01            |  |  |

| 8.0                  | 0.000 52     | 0.013 63            | 0.013 29            | 0.012 82            | 0.018 60            | 0.026 36            |  |  |

| 9.0                  | 0.000 13     | 0.006 93            | 0.007 15            | 0.006 95            | 0.012 79            | 0.019 15            |  |  |

| 10.0                 | 0.000 032 75 | 0.003 43            | 0.003 48            | 0.003 46            | 0.008 25            | 0.014 31            |  |  |

表 2 Viterbi 译码后误码率统计 Table2 Error rate statistics after Viterbi decoding

| Table 2 Error rate Statistics after There's decoding |         |                     |                     |                     |                     |                     |  |  |

|------------------------------------------------------|---------|---------------------|---------------------|---------------------|---------------------|---------------------|--|--|

| $R_{\rm SN}/{ m dB}$                                 | BER     |                     |                     |                     |                     |                     |  |  |

|                                                      | delay 0 | delay of 10 symbols | delay of 20 symbols | delay of 30 symbols | delay of 40 symbols | delay of 50 symbols |  |  |

| 6.5                                                  | 0       | 0.000 857           | 0.000 353           | 0.000 187           | 0.001 032           | 0.001 724           |  |  |

| 7.0                                                  | 0       | 0.000 228           | 0.000 104           | 0.000 053 26        | 0.000 364           | 0.000 650           |  |  |

| 8.0                                                  | 0       | 0.000 034 71        | 0.000 022 51        | 0.000 012 68        | 0.000 062 24        | 0.000 137           |  |  |

| 9.0                                                  | 0       | 0.000 001 114       | 0.000 000 484 3     | 0.000 002 711       | 0.000 031 86        | 0.000 047 71        |  |  |

| 10.0                                                 | 0       | 0.000 000 001 307   | 0.000 000 174 4     | 0.000 000 231 2     | 0.000 000 404 8     | 0.000 001 279       |  |  |

表 3 RS 译码后误码率统计

| Table 3 Error rate statistics after RS decoding |         |                     |                     |                     |                     |                     |  |  |

|-------------------------------------------------|---------|---------------------|---------------------|---------------------|---------------------|---------------------|--|--|

| $R_{\rm SN}/{\rm dB}$                           | BER     |                     |                     |                     |                     |                     |  |  |

|                                                 | delay 0 | delay of 10 symbols | delay of 20 symbols | delay of 30 symbols | delay of 40 symbols | delay of 50 symbols |  |  |

| 6.5                                             | 0       | 0.000 018 79        | 0.000 000 488 7     | 0.000 000 809 4     | 0.000 104           | 0.000 112           |  |  |

| 7.0                                             | 0       | 0.000 000 765 4     | 0.000 000 008 968   | 0.000 000 012 61    | 0.000 002 288       | 0.000 022 52        |  |  |

| 8.0                                             | 0       | 0                   | 0                   | 0                   | 0.000 001 283       | 0.000 000 014 29    |  |  |

| 9.0                                             | 0       | 0                   | 0                   | 0                   | 0                   | 0                   |  |  |

| 10.0                                            | 0       | 0                   | 0                   | 0                   | 0                   | 0                   |  |  |

测试环境下信道包含 1条主径和 1条多径,多径能量为–3 dB,分别测试信噪比为 10 dB,9 dB,8 dB,7 dB,6.5 dB,没有多径及多径时延为 10,20,30,40,50 个符号时的误码率情况,每种条件测试  $2.048\times10^7$  个数据,获得均衡后、Viterbi 译码后、RS 译码后的误码率统计见表 1、表 2、表 3。

表中第 1 列表示  $R_{SN}$ , 第 1 行表示时延(Time Delay, TD),以延时符号个数为单位。

由表 1 可以看出,随着信噪比的下降,均衡后误码率会有较大变化,当信噪比下降到 6.5 dB 时,误码率达到 10<sup>-2</sup>量级;随着多径时延的增大,误码率略有提高。对比表 1 和表 2 可以看出,在总体趋势保持基本一致的情况下 Viterbi 译码后,除 6.5 dB 下时延 40 个和 50 个符号的情况之外,误码率下降到 10<sup>-4</sup>量级,这说明 Viterbi 译码有效地纠正了均衡后系统的错误。对比表 3,RS 译码后在信噪比为 7 dB 以上时,除去时延 50 个符号的情况下,误码率下降到 10<sup>-6</sup>量级,即使在 6.5 dB 的情况下,也能达到 10<sup>-4</sup>量级,显然性能又有显著的提升。

#### 4 结论

本文设计了宽带单载波频域均衡系统并完成 FPGA 实现。实现了 137.5 MHz 载波下 27.5 Mbps 的码元传输速率,并在 MMSE 准则下完成频域均衡,此外添加了卷积码和 RS 码级联编译码。最终在 Virtix-4 芯片上实现整个系统,并分别对均衡后、Viterbi 译码、RS 译码后的误码率性能做了统计和对比,测试结果表明本系统可以很好地实现宽带单载波通信。

#### 参考文献:

- [1] Bernard Sklar,沈连丰,徐平平,等. 数字通信:基础与应用[M]. 2 版. 北京:电子工业出版社,2010. (Bernard Sklar,SHEN Lianfeng,XU Pingping.et al. Digital Communications Fundamentals and Applications[M]. 2nd ed. Beijing:Publishing House of Electronics Industry, 2010.)

- [2] YU Zhu,Letaief K B. Single carrier frequency domain equalization with noise prediction for broadband wireless systems[C]// Global Telecommunications Conference(GLOBECOM '04). [S.l.]:IEEE, 2004,5:3098-3102.

- [3] Dinis R,Montezuma P,Bernardo L. Frequency-domain multipacket detection:a high throughput technique for SC-FDE systems[J]. IEEE Transactions on Wireless Communications, 2009,8(7):3798-3807.

- [4] Falconer D, Ariyavisitakul S L, Benyamin Seeyar A, et al. Frequency domain equalization for single carrier broadband wireless systems[J]. IEEE Communications Magazine, 2002,40(4):58-66.

- [5] 李朝辉. 单载波频域均衡技术研究[D]. 西安:西安电子科技大学, 2012. (LI Zhaohui. Technology research and development of the single carrier frequency domain equalization[D]. Xi'an, China: Xidian University, 2012.)

- [6] 刘谦雷,杨绿溪. 单载波频域均衡与多载波 OFDM 误码性能的理论比较[J]. 电子与信息学报, 2005,27(3):411-414. (LIU Qianlei,YANG Luxi. Theoretical comparison of BER performance between single-carrier frequency-domain equalization and multi-carrier OFDM[J]. Journal of Electronics Information Technology, 2005,27(3):411-414.)

- [7] 吴江,吴伟陵. 未来无线通信中的单载波频域均衡技术[J]. 数据通信, 2004(5):4-7. (WU Jiang, WU Weiling. Single carrier frequency domain equalization technology in future wireless communications[J]. Data Communications, 2004(5):4-7.)

- [8] 桑会平,邓甲昊. 宽带无线通信的单载波频域均衡技术研究[J]. 科技导报, 2009(7):64-69. (SANG Huiping, DENG Jiahao. Single carrier frequency domain equalization technology applied to broadband wireless communications[J]. Science & Technology Review, 2009(7):64-69.)

- [9] 徐健. 单载波高速数据链的抗多径算法和 FPGA 实现[D]. 南京:南京航空航天大学, 2012. (XU Jian. The anti-multipath algorithm for single-carrier high-speed datalinks and the implementation based on FPGA[D]. Nanjing, China: Nanjing University of Aeronautics and Astronautics, 2012.)

- [10] 陈晨,赵民建,陈文正. 单载波频域均衡技术的定时同步研究[J]. 浙江大学学报:工学版, 2007,41(3):445-449. (CHEN Chen,ZHAO Minjian,CHEN Wenzheng. Timing synchronization for SC-FDE[J]. Journal of Zhejiang University:Engineering Science Edition, 2007,41(3):445-449.)

- [11] 陈欣,邱少华. 基于现场可编程门阵列的单载波频域均衡系统[J]. 太赫兹科学与电子信息学报, 2012,10(4):416-420. (CHEN Xin,QU Shaohua. Single carrier-frequency domain equalization system based on FPGA[J]. Journal of Terahertz Science and Electronic Information Technology, 2012,10(4):416-420.)

- [12] 吴金秋. 多途信道条件下单载波信道均衡技术研究[J]. 齐齐哈尔大学学报:自然科学版, 2013,29(4):57-63. (WU Jinqiu. Channel equalization technology research on single carrier system under multiplicity channel[J]. Journal of Qiqihar University:Natural Science Edition, 2013,29(4):57-63.)

- [13] 万慧琳. 多种级联码纠错系统的研究与设计[D]. 南京:南京师范大学, 2007. (WAN Huilin. Research and design of a variety of concatenated code error correcting system[D]. Nanjing, China: Nanjing Normal University, 2007.)

- [14] 温学东. 卷积码编码及其 Viterbi 译码算法的 FPGA 实现[J]. 太赫兹科学与电子信息学报, 2005,3(3):176-178. (WEN Xuedong. FPGA implementation of convolution code encoding and Viterbi decoding algorithm[J]. Journal of Terahertz Science and Electronic Information Technology, 2005,3(3):176-178.)

- [15] 曾湘文. RS 与卷积级联的编解码 FPGA 实现[D]. 成都:电子科技大学, 2010. (ZEN Xiangwen. The FPGA implementation of RS and convolution cascade encoding and decoding[D]. Chengdu, China: University of Electronic Science and Technology of China, 2010.)

- [16] 杨俊平,姚远程,秦明伟. 基于 FPGA 的 RS 码译码器的设计[J]. 电子设计工程, 2013,21(1):24-27. (YANG Junping, YAO Yuancheng,QIN Mingwei. Design of RS decoder based on FPGA[J]. Electronic Design Engineering, 2013,21(1): 24-27.)

- [17] 王波,孙一,冯为,等. 基于 FPGA 的快速 RS 码的实现[J]. 电子测量技术, 2009,32(6):143-147. (WANG Bo,SUN Yi, FENG Wei,et al. Design of fast RS code based on FPGA[J]. Electronic Measurement Technology, 2009,32(6):143-147.)

#### 作者简介:

**杨 刚**(1990-),男,山东省临沂市人, 在读硕士研究生,主要研究方向为数字通信系统. 李 莹(1990-), 女, 陕西省渭南市人, 在读硕士研究生, 主要研究方向为信号处理.

张小飞(1977-),男,江苏省淮安市人,教授,博士生导师,主要研究方向为数字通信、通信信号处理、阵列信号处理、雷达信号处理。email:zhangxiaofei@nuaa.edu.cn.

**徐大专**(1963-),男,江苏省盐城市人,教授,博士生导师,主要研究方向为编码理论、通信信号处理、数字信号处理.